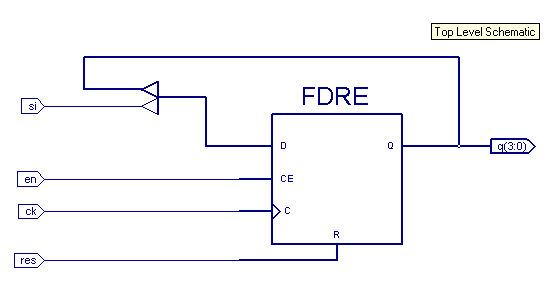

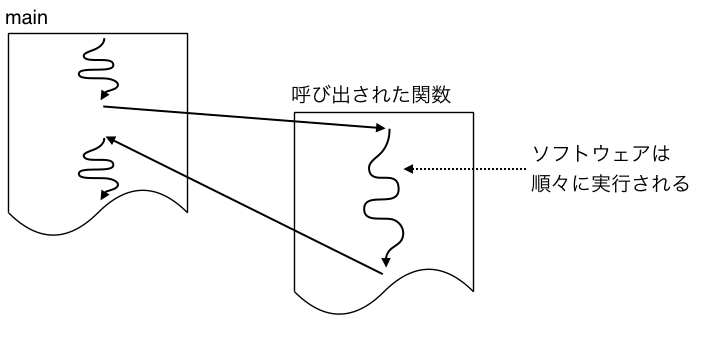

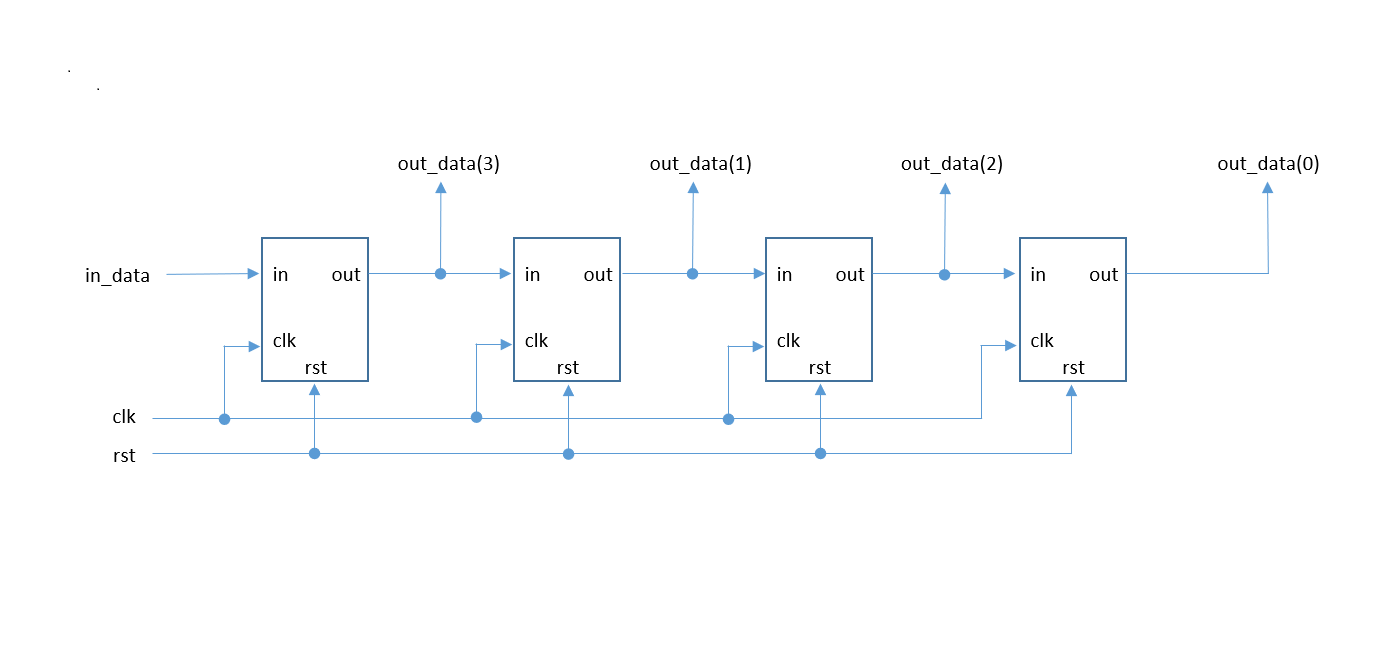

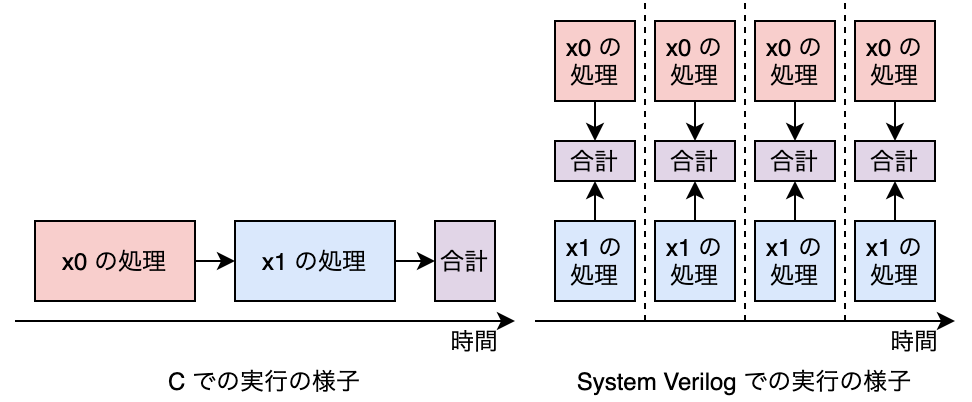

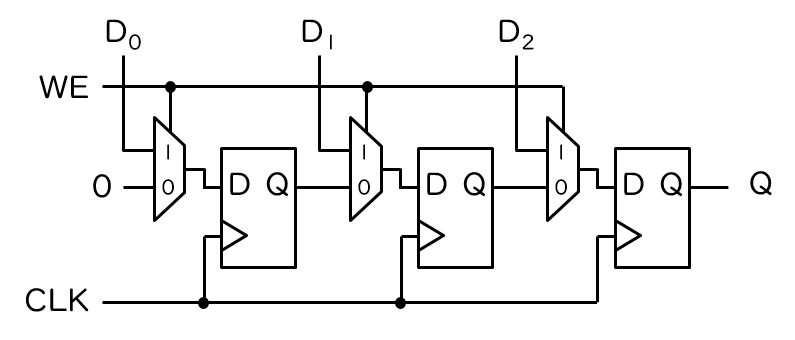

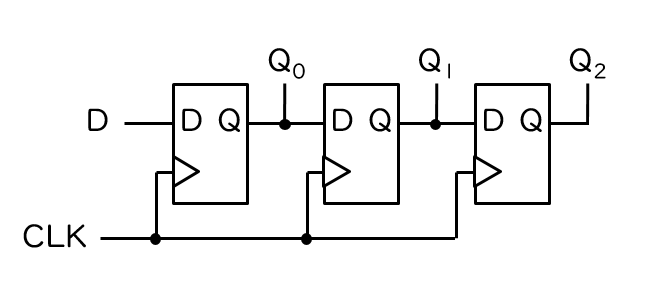

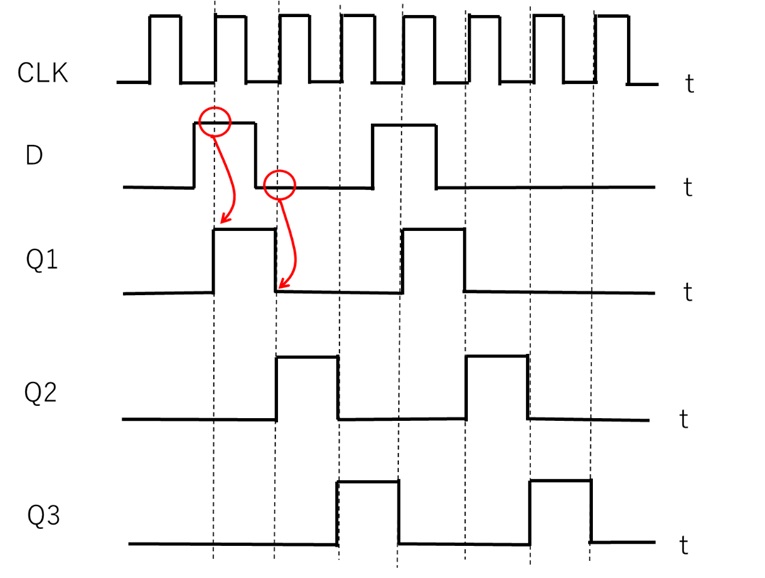

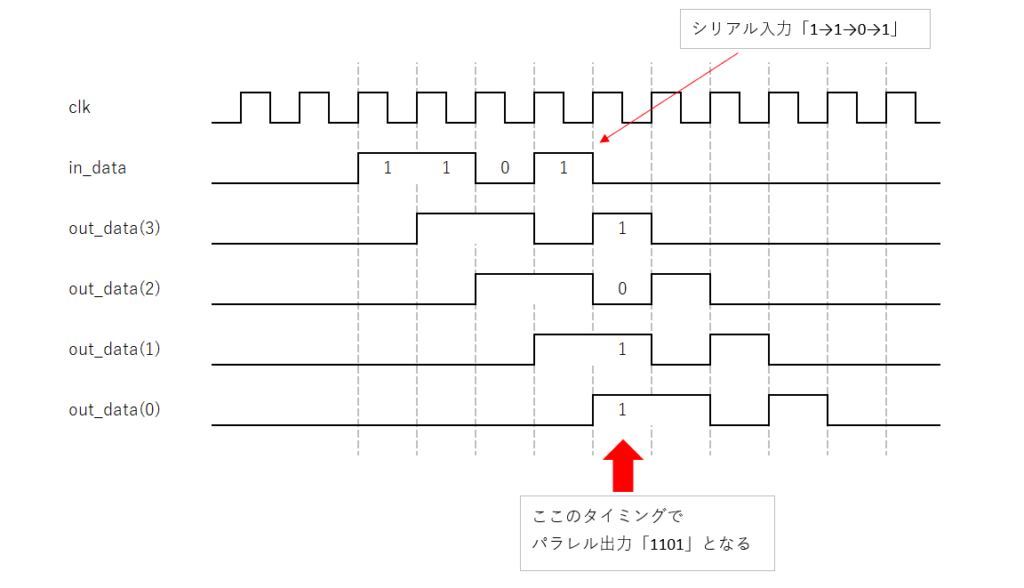

この例では、Verilog HDL における、等間隔のタップを備えた 8ビット幅、64ビット長のシフト・レジスターを説明しています。 合成ツールは、ターゲット・デバイスのアーキテクチャーに応じて

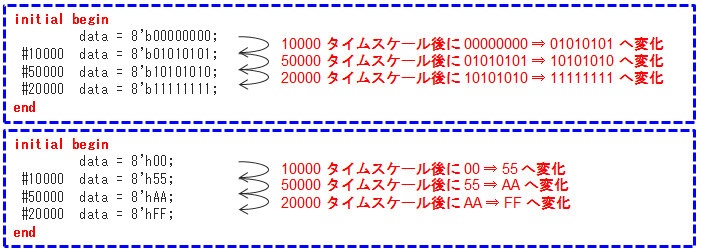

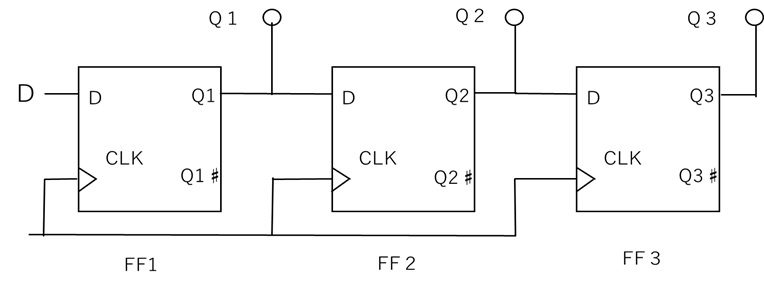

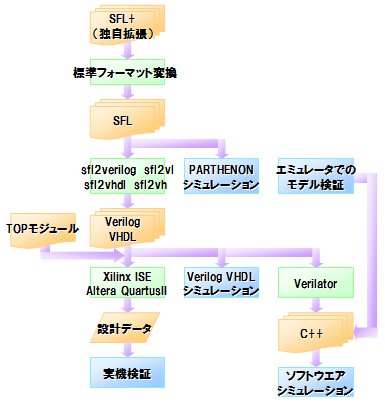

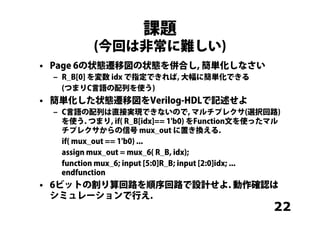

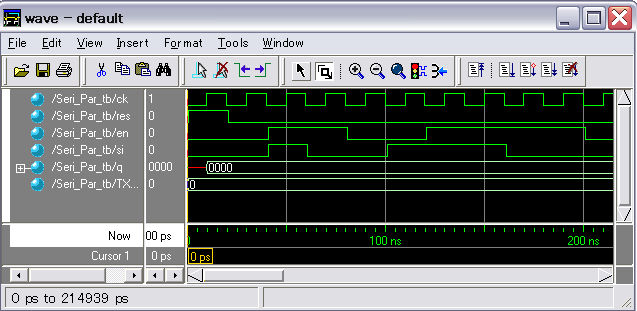

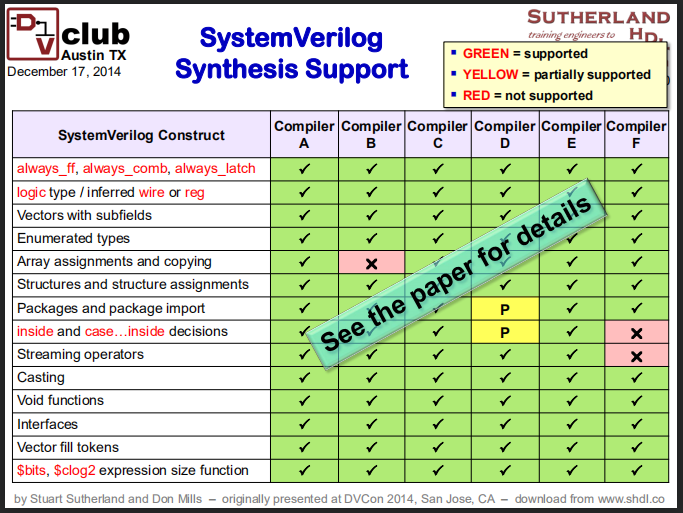

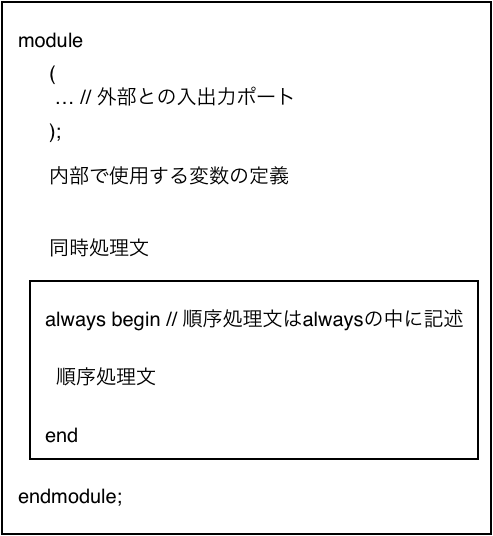

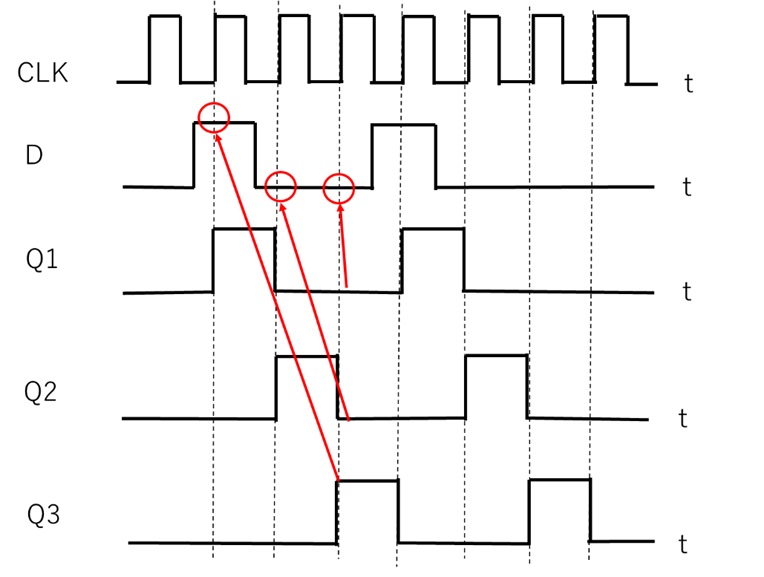

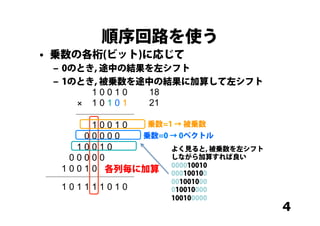

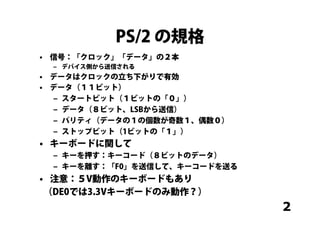

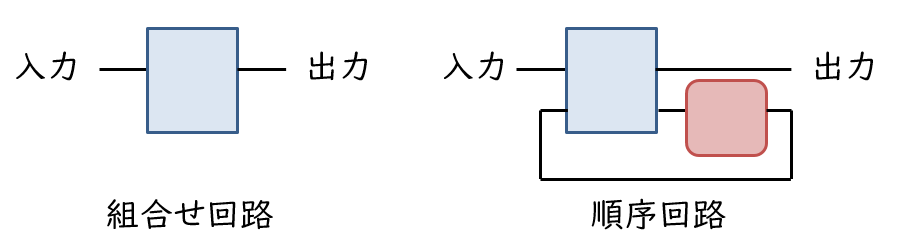

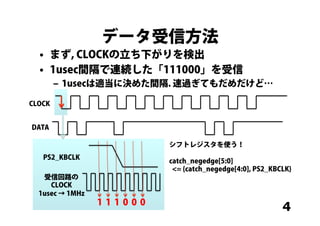

Verilog シフトレジスタ 配列-Multidimensional Array SystemVerilogでは多次元配列を扱えるようになった。 いまさら例を出すまでもないが、8bit長のレジスタを宣言するには、以下のようにしていた。 8bit長のレジスタの、4これが代表的なシフトレジスタの記述法です。 ステートマシン 制御回路の設計でステートマシンは便利な記述です。 例えば下の状態遷移図を持つステートマシンの記述について考えてみます。 動作

Verilog シフトレジスタ 配列のギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

|  | |

| ||

|  | |

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

| ||

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  | |

| ||

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

| ||

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

| ||

|  |  |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  | |

|  |  |

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

| ||

|  |  |

|  | |

「Verilog シフトレジスタ 配列」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  | |

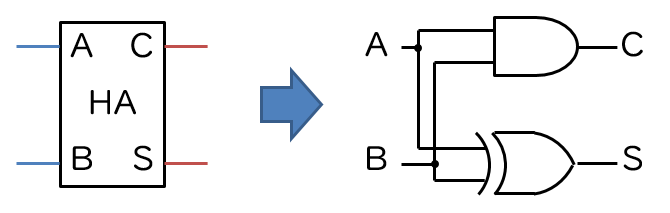

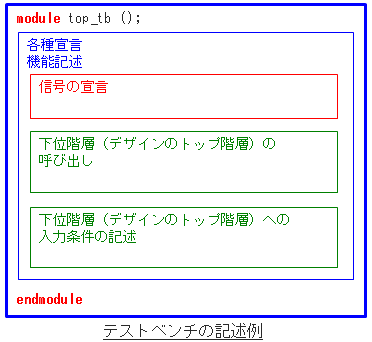

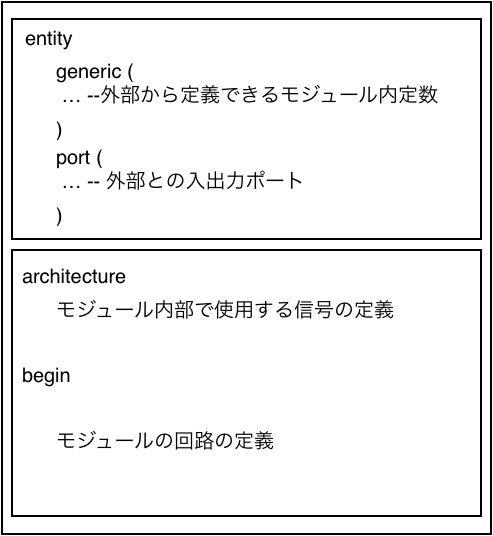

ハードウェア記述言語 組み合わせ回路の記述 順序回路の記述 その他、注意点 エリート官僚VHDL 厳格、几帳面 元々が仕様記述言語で あった アルゴリズム記述言語 ALGOL に端を発しPL/1、 Ada の系 実習1 シフトレジスタの設計 以下のshiftregistervで設計される回路を実習ボードの実装して、その動作を確かめること。 ただし、toplevel entity はshiftregister とする。 入出力の割

Incoming Term: verilog シフトレジスタ 配列,

0 件のコメント:

コメントを投稿